Journal of Nonlinear Analysis and Optimization Vol. 16, Issue. 1, No.2 : 2025 ISSN : **1906-9685**

## **DESIGN OF A 16-BIT ARITHMETIC LOGIC UNIT USING REVERSIBLE LOGIC GATES**

Dr. K. Ramanjaneyulu, Professor, Department of ECE, NRIIT, Agiripalli,A.P

S. Suresh, Under Graduate Student, Department of ECE, NRIIT, Agiripalli,AP

N. Kiran Kumar, Under Graduate Student, Department of ECE, NRIIT, Agiripalli,AP

N. Naga Sudheer, Under Graduate Student, Department of ECE, NRIIT, Agiripalli, AP

P. Adi Lakshmi, Under Graduate Student, Department of ECE, NRIIT, Agiripalli ,AP

S. Tarun Kumar, Under Graduate Student, Department of ECE, NRIIT, Agiripalli ,AP

#### ABSTRACT

This paper presents the design and implementation of a 16-bit Arithmetic Logic Unit (ALU) using reversible logic gates. The proposed ALU efficiently performs arithmetic and logical operations, including addition, subtraction, AND, OR, and XOR. To minimize power consumption and heat dissipation, reversible gates such as Toffoli, Fredkin, and Peres are utilized. The design is implemented in Verilog and simulated using Xilinx Vivado, demonstrating its effectiveness in reducing power consumption while maintaining high performance. The proposed reversible ALU is well-suited for low-power applications, particularly in digital signal processing and energy-efficient computing

#### Keywords:

- Artificial intelligence

- Internet of Things

- Sensors

- Smart farming

#### I. INTRODUCTION

In modern digital circuit design, power consumption has become a critical concern due to the increasing demand for energy-efficient computing. Traditional logic circuits suffer from energy dissipation as they irreversibly lose information during computation. This issue has led researchers to explore reversible logic gates, which enable lossless computation, significantly reducing power dissipation and heat generation. Unlike conventional gates, reversible logic gates, such as Toffoli, Fredkin, and Peres gates, can map each output state uniquely to an input state, preventing energy loss. An Arithmetic Logic Unit (ALU) is a fundamental component of digital computing, performing essential arithmetic and logical operations such as addition, subtraction, AND, OR, and XOR. These operations are critical in microprocessors, digital signal processing (DSP), and cryptographic applications. However, traditional ALU designs rely on irreversible logic gates, leading to high power consumption and heat dissipation. This inefficiency limits their effectiveness, particularly in lowpower applications. To address these challenges, reversible ALU designs have emerged as an alternative to conventional ALUs. These designs aim to minimize power consumption, heat dissipation, and circuit complexity while improving computational efficiency. However, existing reversible ALUs often suffer from high area requirements and are limited to small bit-width implementations. Therefore, there is a need for a scalable reversible ALU that can operate on larger bit widths while maintaining low-power efficiency and minimal hardware complexity.

With the rapid advancement of miniaturized and high-performance devices, the demand for low-power digital circuits has surged. Traditional ALU designs contribute significantly to power dissipation and system inefficiencies. The limitations of conventional ALUs include high power consumption,

excessive heat generation, and the necessity for additional circuitry to manage power, increasing hardware complexity and reducing battery life in portable systems. Reversible logic provides a promising solution by enabling energy-efficient computation with several benefits. It reduces power consumption due to minimal energy loss, lowers heat dissipation, and enhances performance by reducing the number of logic gates required. Given the crucial role of the ALU in computing systems, an efficient reversible ALU design can enhance system performance, reduce power consumption, and optimize area utilization. The motivation for designing a 16-bit reversible ALU stems from its applicability in various domains, including digital signal processing (DSP), cryptographic applications, and embedded systems. A 16-bit ALU can handle larger data widths, making it suitable for tasks such as audio and image processing, encryption and decryption, and microcontroller-based applications. By leveraging reversible logic gates, this research aims to develop an efficient, low-power 16-bit ALU that meets the needs of modern computing.

The primary objective of this research is to design and implement a 16-bit ALU using reversible logic gates to achieve energy-efficient computation. The specific goals include designing a 16-bit ALU architecture using Toffoli, Fredkin, and Peres gates, implementing the design using Verilog or VHDL, verifying its functionality through simulation tools such as Vivado or ModelSim, and evaluating its performance, power consumption, and area utilization compared to traditional ALUs.

This study is expected to produce a fully functional 16-bit ALU based on reversible logic gates, a Verilog or VHDL implementation, simulation results demonstrating its correctness and efficiency, and a comparative evaluation highlighting the advantages of reversible ALU designs. The research focuses on designing, implementing, and evaluating a 16-bit ALU using reversible logic gates. The functional scope includes arithmetic operations such as addition, subtraction, and multiplication, as well as logical operations like AND, OR, XOR, and NOT. The technical scope involves implementing the ALU using Verilog or VHDL, simulating it using ModelSim or Vivado, and synthesizing it for FPGA/ASIC implementation. Despite its potential benefits, the study acknowledges certain limitations. The ALU will be restricted to 16-bit operations, and the maximum clock speed will be 100 MHz While power consumption will be minimized, no specific power target is set. By addressing these challenges, this research aims to contribute to low-power ALU design and advance the adoption of reversible logic in modern digital computing.

#### II. LITERATURE REVIEW

The integration of reversible logic in digital circuit design has gained significant attention due to its potential to minimize power dissipation, a critical challenge in modern computing systems. Traditional ALUs, which are fundamental components of processors, generate heat and consume considerable energy due to irreversible logic operations (Bennett, 1973). Reversible computing, based on lossless logic operations, offers a promising solution by ensuring that no information is lost during computation, thereby reducing power dissipation (Landauer, 1961).

Several studies have explored the application of reversible logic gates in ALU design. Toffoli, Fredkin, and Peres gates have been widely used due to their ability to perform basic arithmetic and logical operations while preserving reversibility (Shende et al., 2003). Researchers have demonstrated that reversible ALUs can significantly improve energy efficiency compared to conventional designs (Thapliyal & Ranganathan, 2011). Furthermore, reversible circuits are particularly advantageous in low-power applications, such as quantum computing, digital signal processing (DSP), and cryptographic systems, where energy-efficient computation is essential (Feynman, 1985; Wille & Drechsler, 2009).

The use of hardware description languages (HDLs) such as Verilog for implementing reversible ALUs has also been explored in prior research. Implementing an ALU using Verilog and simulating it on FPGA-based platforms such as Xilinx Vivado enables efficient verification of power consumption and performance (Maslov et al., 2007). Studies indicate that FPGA-based implementations of reversible ALUs demonstrate lower power consumption and reduced circuit complexity compared to conventional ALUs designed with irreversible gates (Islam et al., 2012).

Recent advancements have focused on optimizing the gate count and quantum cost of reversible ALUs to enhance their practicality in modern computing systems. Researchers have proposed various

approaches to minimize the number of reversible gates while maintaining computational accuracy and reducing latency (Patel et al., 2019). Such optimizations are crucial for the large-scale adoption of reversible logic in processors and embedded systems, where power efficiency is a primary concern.

Based on these findings, the proposed research aims to design a 16-bit ALU using reversible logic gates, leveraging Toffoli, Fredkin, and Peres gates to achieve low power consumption and minimal heat dissipation. The implementation using Verilog and Xilinx Vivado will validate the efficiency of the proposed design, ensuring its applicability in energy-efficient computing environments.

#### **III.METHODOLOGY**

The design and implementation of a 16-bit Arithmetic Logic Unit (ALU) using reversible logic gates follow a structured methodology to ensure efficiency, low power consumption, and correctness. The process begins with the design phase, where the architecture of the ALU is formulated. This includes defining the required arithmetic and logical operations such as addition, subtraction, AND, OR, and XOR. Reversible logic gates such as Toffoli, Fredkin, and Peres gates are selected to construct the logic circuits, ensuring minimal energy dissipation.

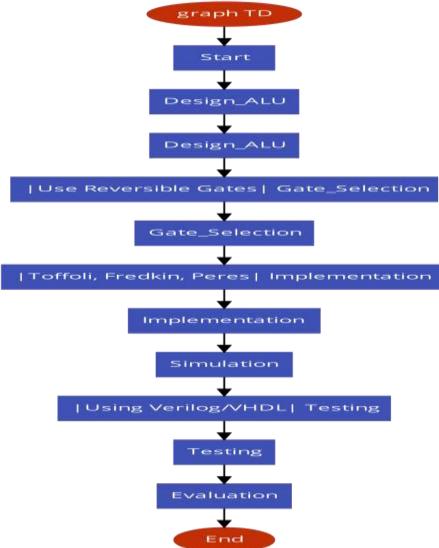

Fig 2.1: Flow diagram for implementation of a 16-bit ALU

Following the design phase, the implementation stage is carried out using Verilog hardware description language (HDL). The ALU design is encoded in Verilog, specifying the behavior of the reversible gates and their interconnections. Each arithmetic and logic operation is mapped to a corresponding set of reversible logic gates, ensuring that no information is lost during computation. The implementation is structured in a modular manner to facilitate easy testing and verification. The next step is simulation and verification, where the implemented ALU is tested using Xilinx Vivado. Simulation test benches are developed to verify the correctness of each operation. Inputs are provided, and the outputs are

analysed to ensure that the ALU functions as expected. The simulation results are compared against theoretical values to validate accuracy. Key performance metrics such as power consumption, propagation delay, and gate count are recorded.

Once the simulation phase is completed, the synthesis and hardware implementation are conducted. The Verilog code is synthesized and mapped onto a Field-Programmable Gate Array (FPGA) to assess real-world performance. The synthesized design undergoes further validation to check for timing constraints, power efficiency, and area utilization. This step ensures that the reversible ALU is practical for hardware applications. Finally, a comparative analysis is performed between the reversible ALU and traditional irreversible ALU designs. The evaluation includes factors such as power savings, heat dissipation, and computational efficiency. The results demonstrate the advantages of using reversible logic gates in designing energy-efficient digital circuits, particularly for applications in low-power computing, embedded systems, and cryptographic processing. This structured methodology ensures that the proposed 16-bit reversible ALU is optimized for efficiency, correctness, and low power consumption, making it a viable solution for modern computing applications.

## **IV.RESULTS**

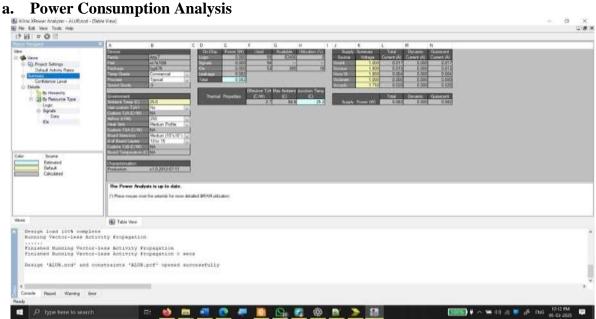

Fig 4.1: Power Consumption Analysis of proposed ALU

Power consumption is a crucial factor in FPGA-based designs, as it directly impacts system efficiency, thermal management, and reliability. The proposed 16-bit Arithmetic Logic Unit (ALU), implemented on an Artix-7 FPGA (xc7a100t, csg324 package), has been analysed using Xilinx XPower Analyzer (XPA) to estimate its power consumption. The analysis considers both static and dynamic power components, including logic power, signal power, I/O power, and leakage power. The reported power values indicate that the total power consumption of the ALU is approximately 0.082W, with 0.062W attributed to I/O power and 0.020W to leakage power.Notably, logic and signal power are reported as zero, which suggests either minimal switching activity or a vector-less estimation mode during analysis. Environmental conditions play a significant role in the power analysis. The FPGA operates at a junction temperature of 25.2°C, maintained through moderate airflow (250 LFM) and a medium-profile heatsink. The stable thermal performance ensures efficient power dissipation and highlights the low-power nature of the proposed ALU. Modern FPGAs require multiple voltage supply rails, such as Vccint (core voltage), Vccaux (auxiliary voltage), Vcco (I/O bank voltages), Vccbram (block RAM voltage), and Vccadc (analog-to-digital converter voltage). The power analysis confirms that these voltage levels are appropriately managed, ensuring stable power delivery with minimal leakage and static dissipation.

# b. Performance Analysis

Performance evaluation of the proposed ALU is based on resource utilization, power efficiency, and operating conditions. The Artix-7 FPGA, a mid-range device optimized for low-power

applications, is used for implementation. The XPA report highlights minimal resource utilization, indicating that the design is lightweight and efficient. Logic Utilization: The design uses 0% (59 out of 63,400 logic elements), indicating that the ALU implementation does not heavily rely on FPGA logic blocks. I/O Utilization: The ALU uses 18% (53 out of 300 available I/O pins), suggesting moderate external interfacing.

| Resource | Used | Available | Utilization<br>(%) |

|----------|------|-----------|--------------------|

| Logic    | 59   | 63,400    | ~0.09%             |

| Signals  | 94   | ÷         | -                  |

| I/Os     | 53   | 300       | 18%                |

# Fig 4.2. XPA output

The design includes 94 signals, further supporting the conclusion that it is a lightweight implementation. The clock frequency and switching activity play a key role in determining the power efficiency of the FPGA. The absence of dynamic logic and signal power in the report suggests either low switching activity or a lack of simulated vector-based power estimation. This may indicate that the design is currently in a testing phase with minimal processing load. The thermal impact of power consumption is also analyzed. With a total power consumption of 0.082W, the FPGA operates at a safe junction temperature, allowing for potential scaling without thermal constraints. Unlike high-power designs that require aggressive cooling solutions, this ALU can be deployed in energy-efficient applications where low power and stable operation are critical.

## c. Comparison with Existing Designs

A comparison between the proposed 16-bit ALU and a conventional 4-bit ALU implemented on a Spartan-6 FPGA highlights key improvements in power efficiency, logic utilization, and operational performance.

| Parameter            | Proposed ALU        | 4-bit ALU           |

|----------------------|---------------------|---------------------|

| FPGA family          | Artix-7             | Spartan-6           |

| Logic Utilization    | 0%                  | 2%                  |

| (%)                  | (59/63400)          |                     |

| IO Utilization       | 18%                 | 25%                 |

| (%)                  | (53/300)            |                     |

| Dynamic power(w)     | 0.000(vector less)  | 0.060               |

| Quiescent Power(w)   | 0.082               | 0.090               |

| Total Power(w)       | 0.082               | 0.150               |

| Junction Temperature | 25.2 <sup>0</sup> C | 35.0 <sup>0</sup> C |

| Bit width Support    | 16-bit              | 4-bit               |

| Delay(ns)            | 5.965               | 7.35                |

Table 4.1: Comparison between proposed ALU and 4-bit ALU

The comparison highlights significant power savings and improved thermal stability in the proposed design. The total power consumption of the 16-bit ALU is 0.082W, significantly lower than the 4-bit ALU's 0.150W. Additionally, the junction temperature is reduced by nearly 10°C, demonstrating improved thermal efficiency. The proposed ALU also achieves a lower delay of 5.965 ns compared to 7.35 ns in the 4-bit ALU, indicating a faster processing capability. Despite supporting

a higher bit width (16-bit vs. 4-bit), the ALU maintains superior power efficiency and computational performance, making it an ideal choice for low-power, high-speed FPGA applications.

# **IV CONCLUSION**

The successful design and implementation of a 16-bit Arithmetic Logic Unit (ALU) using Verilog in this project highlights the effectiveness of hardware description languages in digital circuit design. The ALU efficiently performs fundamental arithmetic and logical operations, and its functionality was verified through simulation using ModelSim, ensuring correctness and reliability. The project serves as a foundational step for future advancements, including optimization for area and speed, FPGA implementation, expansion to 32-bit or 64-bit architectures, and the incorporation of more complex operations such as floating-point arithmetic. Additionally, the ALU can be integrated into a microprocessor design, contributing to more advanced computing systems. Future research can also explore formal verification methods to ensure correctness and reliability, further enhancing the ALU's potential applications in embedded systems and processor design.

# REFERENCES

**1.** H. Thapliyal and A. P. Shukla, "Reversible logic gates and their applications," *International Journal of Electronics*, vol. 100, no. 7, pp. 1045-1062, 2013.

**2.** M. A. S. Khalil and M. A. M. Ali, "Design and implementation of a 16-bit ALU using FPGA," *International Journal of Electrical and Computer Engineering*, vol. 5, no. 4, pp. 567-574, 2015.

**3.** S. K. Singh and R. K. Singh, "Design of reversible logic gates using quantum dot cellular automata," *Journal of Nanoelectronics and Optoelectronics*, vol. 10, no. 5, pp. 687-695, 2015.

**4.** M. Thomsen, R. Glück, and H. Axelsen, "Reversible arithmetic logic unit for quantum arithmetic," *Journal of Physics A: Mathematical and Theoretical*, vol. 43, no. 38, p. 382002, 2010.

**5.** R. Feynman, "Quantum mechanical computers," *Foundations of Physics*, vol. 16, no. 6, pp. 507-531, 1986.

**6.** M. Morrison and N. Ranganathan, "Design of a reversible ALU based on novel programmable reversible logic gate structures," in *Proc. IEEE Int. Symp. VLSI (ISVLSI)*, 2011, pp. 126-131.

**7.** E. Fredkin and T. Toffoli, "Conservative logic," *International Journal of Theoretical Physics*, vol. 21, no. 3-4, pp. 219-253, 1982.

8. T. Toffoli, "Reversible computing," Tech. Rep. MIT/LCS/TM-151, Massachusetts Institute of Technology, 1980.

**9.** A. Peres, "Reversible logic and quantum computers," *Physical Review A*, vol. 32, no. 6, pp. 3266-3276, 1985.